# **BECKHOFF**

# CB4057

# Manual

rev. 1.4

# **Contents**

| 0 | Doc   | ument History      |                                       | 5  |

|---|-------|--------------------|---------------------------------------|----|

| 1 | Intro | duction            |                                       | 6  |

|   | 1.1   | Notes on the Docur | mentation                             | 6  |

|   | 1.1.  | Liability Condit   | itions                                | 6  |

|   | 1.1.  | 2 Copyright        |                                       | 6  |

|   | 1.2   |                    |                                       |    |

|   | 1.2.  | •                  |                                       |    |

|   | 1.2.  | 2 Description of   | Safety Symbols                        | 7  |

|   | 1.3   | •                  | easures                               |    |

|   | 1.3.  | •                  | oligation to Exercise Diligence       |    |

|   | 1.3.  | •                  | lations Depending on the Machine Type |    |

|   | 1.3.  | _                  | uirements                             |    |

|   | 1.4   | ·                  |                                       |    |

| 2 |       | •                  |                                       |    |

|   | 2.1   | Features           |                                       | 10 |

|   | 2.2   |                    | Documents                             |    |

| 3 |       | •                  |                                       |    |

| _ | 3.1   |                    |                                       |    |

|   | 3.2   | •                  |                                       |    |

|   | 3.3   |                    |                                       |    |

|   | 3.4   | •                  |                                       |    |

|   | 3.5   | •                  |                                       |    |

|   | 3.6   | PCI/104-Express B  | Bus                                   | 22 |

|   | 3.7   |                    | Card                                  |    |

|   | 3.8   | VGA                |                                       | 25 |

|   | 3.9   | LCD                |                                       | 26 |

|   | 3.10  | Audio              |                                       | 28 |

|   | 3.11  |                    |                                       |    |

|   | 3.12  | LAN                |                                       | 31 |

|   | 3.13  | SATA Interfaces    |                                       | 32 |

|   | 3.14  |                    |                                       |    |

|   | 3.15  | COM3 and COM4      |                                       | 34 |

|   | 3.16  |                    | PT                                    |    |

|   | 3.17  |                    |                                       |    |

|   | 3.18  |                    | ns                                    |    |

| 4 | Stat  | •                  |                                       |    |

|   | 4.1   | HD LED             |                                       | 38 |

|   | 4.2   | RGB LED            |                                       | 39 |

| 5 | BIO   | S Settings         |                                       | 40 |

|   | 5.1   | •                  | Use                                   |    |

|   | 5.2   | •                  |                                       |    |

|   | 5.3   | •                  | eatures                               |    |

|   | 5.3.  |                    | ls                                    |    |

|   | 5.4   | Advanced BIOS Fe   | eatures                               | 43 |

|   | 5.4.  | CPU Feature        |                                       | 45 |

|   | 5.4.  | 2 Hard Disk Boo    | ot Priority                           | 46 |

|   |       |                    |                                       |    |

# Contents

|   | 5.5  | Advanced Chipset Features                     | 47 |

|---|------|-----------------------------------------------|----|

|   | 5.5. | .1 PCI Express Root Port Function             | 48 |

|   | 5.6  | Integrated Peripherals                        | 49 |

|   | 5.6. | .1 OnChip IDE Devices                         | 50 |

|   | 5.6. | 2 SuperIO Devices                             | 51 |

|   | 5.6. | .3 USB Device Setting                         | 52 |

|   | 5.7  | Power Management Setup                        | 53 |

|   | 5.8  | PnP/PCI Configuration                         | 55 |

|   | 5.8. | .1 IRQ Resources                              | 57 |

|   | 5.9  | PC Health Status                              | 58 |

|   | 5.10 | Load Fail-Safe Defaults                       | 59 |

|   | 5.11 | Load Optimized Defaults                       | 59 |

|   | 5.12 | Set Password                                  | 59 |

|   | 5.13 | Save & Exit Setup                             | 59 |

|   | 5.14 | Exit Without Saving                           | 59 |

| 6 | BIO  | S update                                      | 60 |

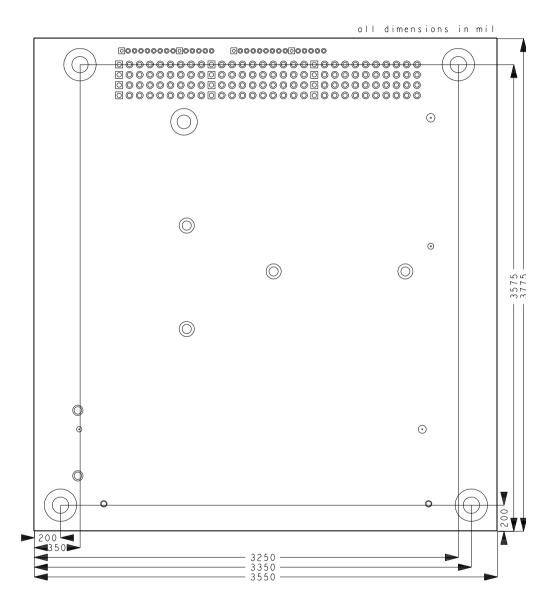

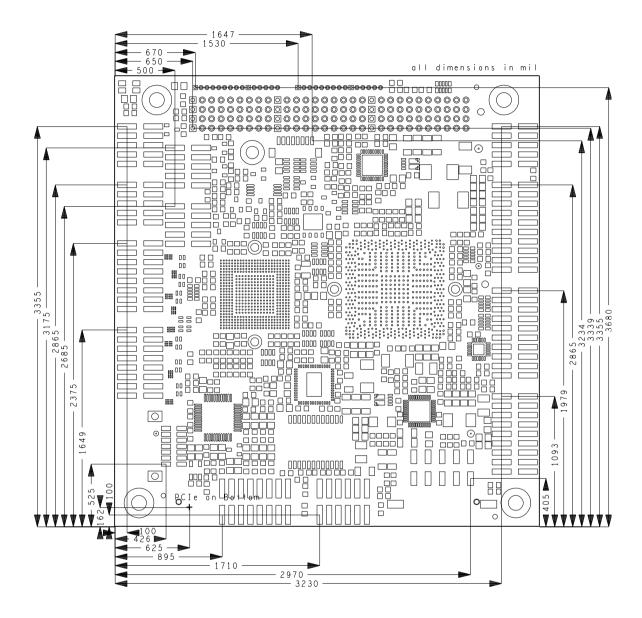

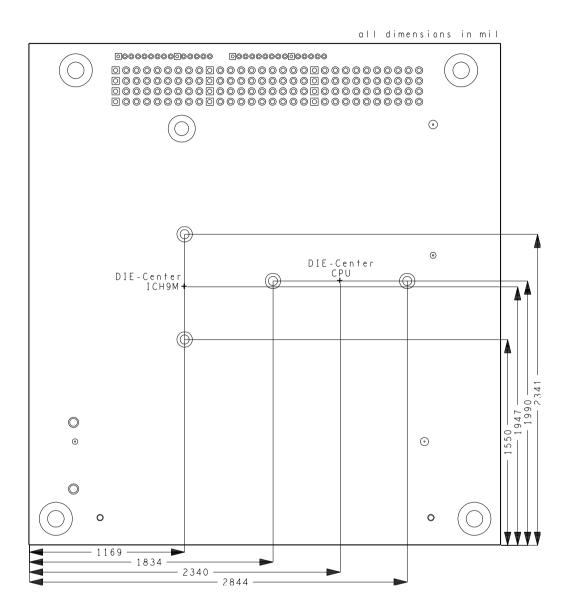

| 7 | Med  | chanical Drawing                              | 61 |

|   | 7.1  | PCB: Mounting Holes                           | 61 |

|   | 7.2  | PCB: Pin 1 Dimensions                         | 62 |

|   | 7.3  | PCB: Heat Sink                                | 63 |

| 8 | Tec  | chnical Data                                  |    |

|   | 8.1  | Electrical Data                               | 64 |

|   | 8.2  | Environmental Conditions                      | 64 |

|   | 8.3  | Thermal Specifications                        |    |

| 9 | Sup  | pport and Service                             |    |

|   | 9.1  | Beckhoff's Branch Offices and Representatives |    |

|   | 9.2  | Beckhoff Headquarters                         |    |

|   | 9.2. | • • • • • • • • • • • • • • • • • • • •       |    |

|   | 9.2. |                                               |    |

| I |      | nex: Post-Codes                               |    |

| Ш |      | nex: Resources                                |    |

|   |      | O Range                                       |    |

|   |      | lemory Range                                  |    |

|   |      | nterrupt                                      |    |

|   | D P  | CI Devices                                    | 71 |

|   | E S  | MB Devices                                    | 71 |

# 0 Document History

| Version | Changes                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1     | first pre-release                                                                                                                                                                    |

| 1.0     | first released version                                                                                                                                                               |

| 1.1     | <ul> <li>new photographs</li> <li>now D525-only</li> <li>4GB max RAM</li> <li>added notes concerning memory frequency and RS485 mode</li> <li>minor changes and additions</li> </ul> |

| 1.2     | <ul> <li>bottom photo now also showing mPCle socket</li> <li>symbols for LAN and Audio headers rotated by 180°</li> </ul>                                                            |

| 1.3     | - improved output quality of dimensional drawings                                                                                                                                    |

| 1.4     | - chapter 3.2: defined adapter card                                                                                                                                                  |

# Note

All company names, brand names, and product names referred to in this manual are registered or unregistered trademarks of their respective holders and are, as such, protected by national and international law.

# 1 Introduction

**Chapter:** Introduction

#### 1.1 Notes on the Documentation

This description is only intended for the use of trained specialists in control and automation engineering who are familiar with the applicable national standards. It is essential that the following notes and explanations are followed when installing and commissioning these components.

#### 1.1.1 Liability Conditions

The responsible staff must ensure that the application or use of the products described satisfy all the requirements for safety, including all the relevant laws, regulations, guidelines and standards. The documentation has been prepared with care. The products described are, however, constantly under development. For that reason the documentation is not in every case checked for consistency with performance data, standards or other characteristics. None of the statements of this manual represents a guarantee (Garantie) in the meaning of § 443 BGB of the German Civil Code or a statement about the contractually expected fitness for a particular purpose in the meaning of § 434 par. 1 sentence 1 BGB. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made on the basis of the data, diagrams and descriptions in this documentation.

#### 1.1.2 Copyright

© This documentation is copyrighted. Any reproduction or third party use of this publication, whether in whole or in part, without the written permission of Beckhoff Automation GmbH, is forbidden.

Safety Instructions Chapter: Introduction

# 1.2 Safety Instructions

Please consider the following safety instructions and descriptions. Product specific safety instructions are to be found on the following pages or in the areas mounting, wiring, commissioning etc.

#### 1.2.1 Disclaimer

All the components are supplied in particular hardware and software configurations appropriate for the application. Modifications to hardware or software configurations other than those described in the documentation are not permitted, and nullify the liability of Beckhoff Automation GmbH.

# 1.2.2 Description of Safety Symbols

The following safety symbols are used in this documentation. They are intended to alert the reader to the associated safety instructions.

#### **ACUTE RISK OF INJURY!**

If you do not adhere to the safety advise next to this symbol, there is immediate danger to life and health of individuals!

### RISK OF INJURY!

If you do not adhere to the safety advise next to this symbol, there is danger to life and health of individuals!

# HAZARD TO INDIVIDUALS, ENVIRONMENT, DEVICES, OR DATA!

If you do not adhere to the safety advise next to this symbol, there is obvious hazard to individuals, to environment, to materials, or to data.

#### NOTE OR POINTER

This symbol indicates information that contributes to better understanding.

#### **Chapter:** Introduction

# 1.3 Essential Safety Measures

#### 1.3.1 Operator's Obligation to Exercise Diligence

The operator must ensure that

- o the product is only used for its intended purpose

- the product is only operated in sound condition and in working order

- the instruction manual is in good condition and complete, and always available for reference at the location where the products are used

- o the product is only used by suitably qualified and authorised personnel

- the personnel is instructed regularly about relevant occupational safety and environmental protection aspects

- the operating personnel is familiar with the operating manual and in particular the safety notes contained herein

# 1.3.2 National Regulations Depending on the Machine Type

Depending on the type of machine and plant in which the product is used, national regulations governing the controllers of such machines will apply, and must be observed by the operator. These regulations cover, amongst other things, the intervals between inspections of the controller. The operator must initiate such inspections in good time.

#### 1.3.3 Operator Requirements

Read the operating instructions

All users of the product must have read the operating instructions for the system they work with.

System know-how

All users must be familiar with all accessible functions of the product.

Functional Range Chapter: Introduction

# 1.4 Functional Range

# NOTE

The descriptions contained in the present documentation represent a detailed and extensive product description. As far as the described motherboard was acquired as an integral component of an Industrial PC from Beckhoff Automation GmbH, this product description shall be applied only in limited scope. Only the contractually agreed specifications of the corresponding Industrial PC from Beckhoff Automation GmbH shall be relevant. Due to several models of Industrial PCs, variations in the component placement of the motherboards are possible. Support and service benefits for the built-in motherboard will be rendered by Beckhoff Automation GmbH exclusively as specified in the product description (inclusive operation system) of the particular Industrial PC.

Chapter: Overview Features

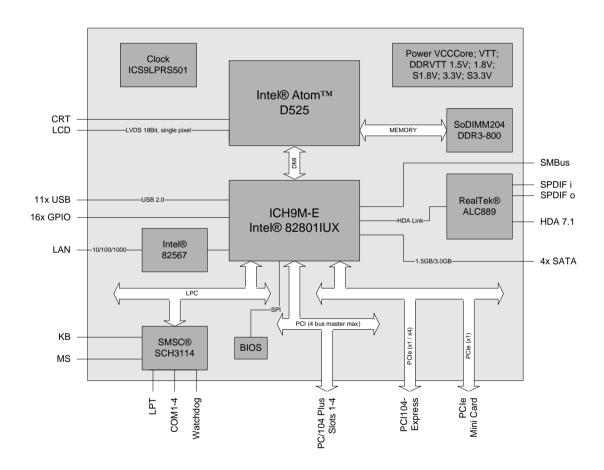

#### 2 Overview

#### 2.1 Features

The CB4057 is a highly complex computer motherboard in the PC/104™ form factor, complying with the state-of-the-art "PCI/104-Express™" standard. It's based on Intel®'s Atom® D525 CPUs combined with the ICH9M-E chip (SFF). Modern DDR3 technology provides top-notch memory performance, accomodating up to 4 GByte of RAM (DDR3-800) via SO-DIMM204. PCI bus and PCI-Express are available through the PC/104-Plus and PCI/104-Express Type 2 connectors respectively, giving system builders a great deal of flexibility as far as expansion cards are concerned. An optional PCIe Mini Card connector adds to that picture. Additional onboard peripheral devices include four serial interfaces, one Gigabit Ethernet interface (LAN), up to four SATA channels, an audio interface (HDA 7.1), up to eleven USB channels and CRT and LVDS/TFT support. There are also 16 discrete programmable GPIO signals available.

- Processor Intel® Atom® D525 (Dualcore, 1.8 GHz, 13W TDP)

- o Chipset Intel® ICH9M-E (SFF)

- o SO-DIMM204 socket for one DDR3-800 module of up to 4 GByte

- o Four serial interfaces COM1-4

- LAN interface Ethernet 10/100/1000 (Base-T)

- o Four SATA channels (two of which on the PCI104-Express connector)

- o PS2 keyboard / mouse interface

- LPT interface

- Up to eleven USB 2.0 interfaces (two on PCI104-Express connector, one on Mini Card)

- o AWARD BIOS 6.10

Features Chapter: Overview

- CRT connection

- o LCD connection via LVDS 18Bit (single pixel)

- HDA compatible sound controller with SPDIF in and out

- RTC with external CMOS battery

- PCI bus via PC/104-Plus (max. four master devices)

- o PCI-Express bus via PCI/104-Express connector (type 2, four x1 lanes)

- o PCI-Express Mini Card connector (option, one x1 lane)

- 16x GPIO

- 5V and 12V supply voltage

- o Size: 96 mm x 90 mm

#### Chapter: Overview

# 2.2 Specifications and Documents

In making this manual and for further reading of technical documentation, the following documents, specifications and web-pages were used and are recommended.

PC/104™ Specification Version 2.5 www.pc104.org

PC/104-Plus™ Specification Version 2.3 www.pc104.org

PCI104-Express™ Specification Version 1.1 www.pc104.org

PCI-Express® Mini Card Specification Version 1.2 www.pcisig.com

PCI Specification Version 2.3 and 3.0 www.pcisig.com

ACPI Specification Version 3.0 www.acpi.info

ATA/ATAPI Specification Version 7 Rev. 1 www.t13.org

USB Specifications www.usb.org

SM-Bus Spedifidation Version 2.0 www.smbus.org

Intel®-Chip Description Atom® D425/D525 www.intel.com

Intel® Chip Description Intel® ICH9 Datasheet www.intel.com

Intel® Chip Description 82567 Datasheet www.intel.com

SMSC® Chip Description SCH3114 Datasheet www.smsc.com

IDT® Chip Description ICS9LPRS501SKLF Datasheet www.idt.com

Realtek® Chip Description ALC889 Datasheet www.realtek.com.tw

# 3 Connectors

This section describes all the connectors found on the CB4057.

# **CAUTION**

For most interfaces, the cables must meet certain requirements. For instance, USB 2.0 requires twisted and shielded cables to reliably maintain full speed data rates. Restrictions on maximum cable length are also in place for many high speed interfaces and for power supply. Please refer to the respective specifications and use suitable cables at all times.

**Chapter:** Connectors

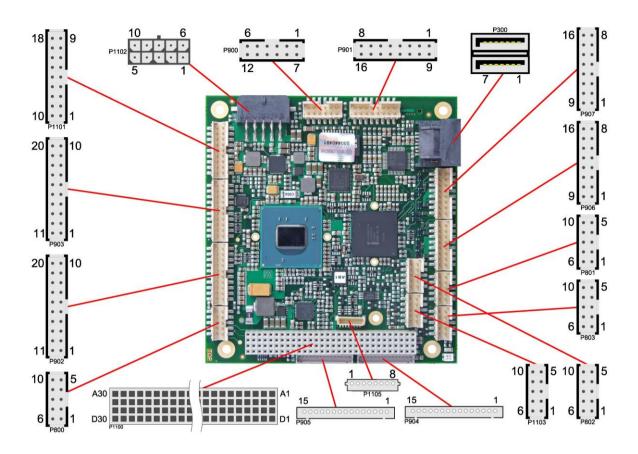

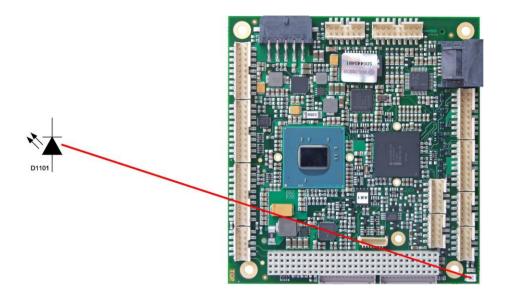

Chapter: Connectors Connector Map

# 3.1 Connector Map

Please use the connector map below for quick reference. Only connectors on the component side are shown. For more information on each connector refer to the table below.

| Ref-No.   | Function                 | Page  |

|-----------|--------------------------|-------|

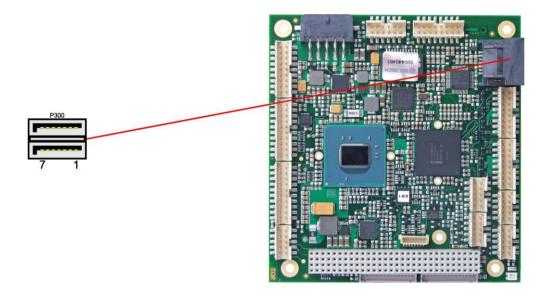

| P300      | "SATA Interfaces"        | p. 32 |

| U400*     | "Memory"                 | p. 17 |

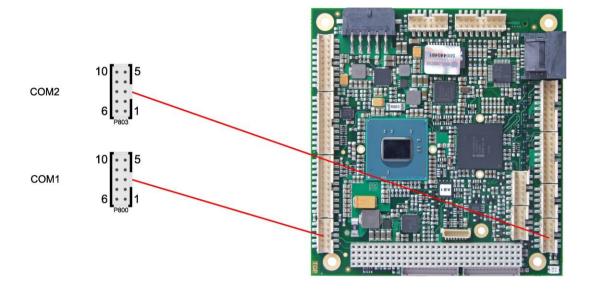

| P800/P803 | "COM1 and COM2"          | p. 33 |

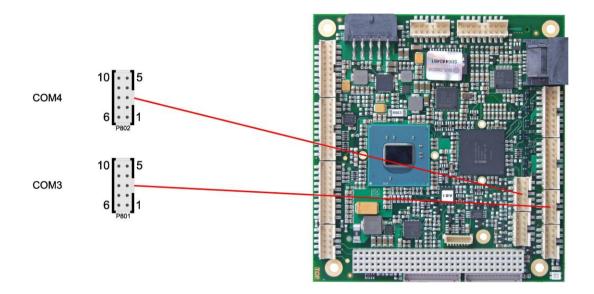

| P801/P802 | "COM3 and COM4"          | p. 34 |

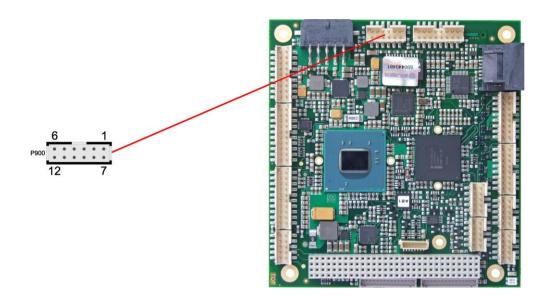

| P900      | "LAN"                    | p. 31 |

| P901      | "Audio"                  | p. 28 |

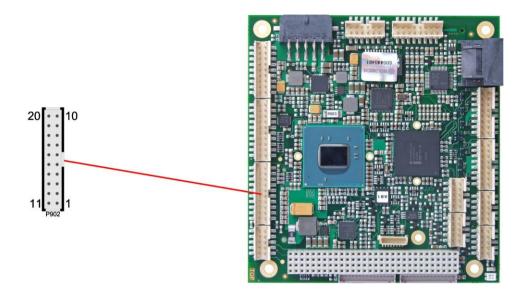

| P902      | "Parallel Interface LPT" | p. 35 |

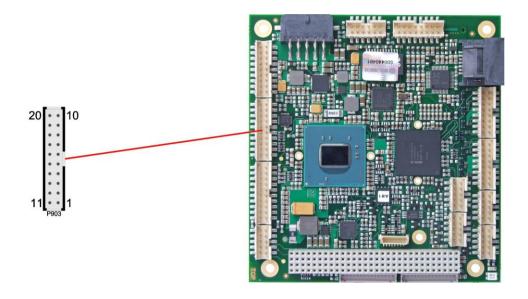

| P903      | "GPIO"                   | p. 36 |

| P904/P905 | "LCD"                    | p. 26 |

| P906/P907 | "USB"                    | p. 29 |

| P1000     | "PCI/104-Express Bus"    | p. 22 |

| P1001*    | "PCI-Express Mini Card"  | p. 24 |

| P1100     | "PC/104-Plus Bus"        | p. 20 |

| P1101     | "System/SM-Bus"          | p. 16 |

| P1102     | "Power Supply"           | p. 15 |

| P1103     | "VGA"                    | p. 25 |

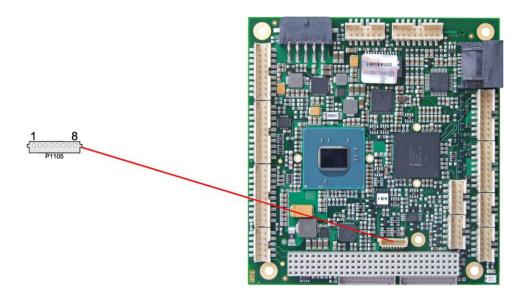

| P1105     | "Monitoring Functions"   | p. 37 |

<sup>\*</sup> not in the picture above (cf. bottom side of board)

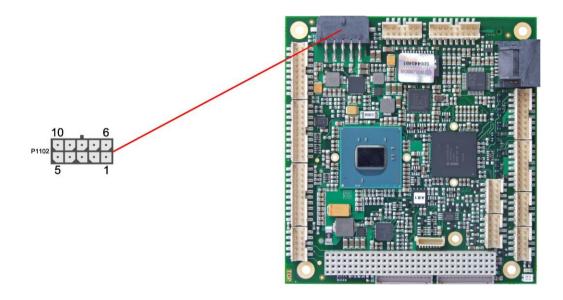

Power Supply Chapter: Connectors

# 3.2 Power Supply

The power supply of the hardware module is realized via a 2x5-pin connector (Molex PS 43045-10xx, mating connector: Molex PS 43025-10xx). The 12V input can optionally be tied to 5V if 12V is not required by an attached PCI or PCIe adapter board. It should not, however, be left unconnected.

#### **CAUTION**

The CB4057 includes circuitry that will notify an intelligent power supply to shut down if the processor reaches a critical temperature. This is achieved by deasserting the (low-active) PS\_ON# signal found on the SM-Bus connector. When PS\_ON# is no longer pulled low, an intelligent power supply would take this as a signal to shut down power. For this to work, PS\_ON# must be connected to the power supply's PS\_ON input. If PS\_ON# is not otherwise connected, the CB4057 can be damaged beyond repair if a thermal shutdown event occurs. In rare instances, if power is not shut down, the board will continue to heat up until failure occurs.

#### NOTE

Since this is a 90 degree connector, the symbol in the drawing below represents the connector face as seen from the side (PCB on bottom) rather than from above.

| Description    | Name | Р | in | Name | Description       |

|----------------|------|---|----|------|-------------------|

| 12 volt supply | 12V  | 1 | 6  | 12V  | 12 volt supply    |

| ground         | GND  | 2 | 7  | GND  | ground            |

| ground         | GND  | 3 | 8  | SVCC | standby-supply 5V |

| ground         | GND  | 4 | 9  | GND  | ground            |

| 5 volt supply  | VCC  | 5 | 10 | VCC  | 5 volt supply     |

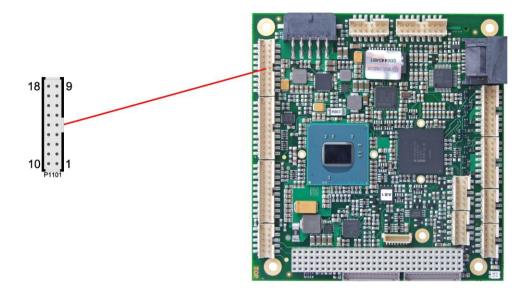

Chapter: Connectors System/SM-Bus

# 3.3 System/SM-Bus

Both SM-Bus signals, and signals for PS/2 keyboard, PS/2 mouse and speaker are provided through a 2x9pin connector (FCI 98424-G52-18LF, mating connector e.g. FCI 90311-018LF). For the #PSON signal, please refer to the cautionary note in the chapter "Power Supply" (p. 15).

Pinout 2x9pin connector:

| Description         | Name    |   | Pin | Name      | Description     |

|---------------------|---------|---|-----|-----------|-----------------|

| speaker to 5V       | SPEAKER | 1 | 10  | GND       | ground          |

| reset to ground     | RSTBTN# | 2 | 11  | N/C       | reserved        |

| keyboard data       | KDAT    | 3 | 12  | KCLK      | keyboard clock  |

| mouse data          | MDAT    | 4 | 13  | MCLK      | mouse clock     |

| battery             | BATT    | 5 | 14  | VCC       | 5 volt supply   |

| power supply on     | PS-ON#  | 6 | 15  | SMBCLK    | SMB clock       |

| standby supply 3.3V | S3.3V   | 7 | 16  | SMBDAT    | SMB data        |

| power button        | PWRBTN# | 8 | 17  | SMBALERT# | SMB alert       |

| ground              | GND     | 9 | 18  | 3.3V      | 3.3 volt supply |

Memory Chapter: Connectors

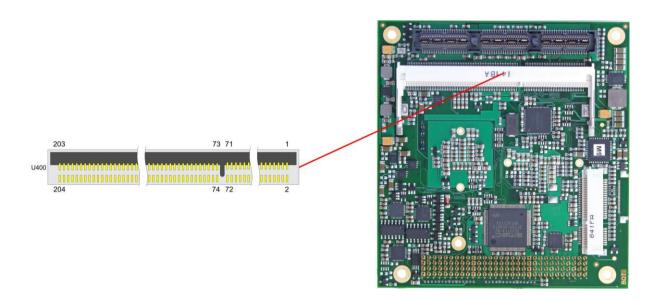

# 3.4 Memory

There is one conventional SO-DIMM204 socket available to equip the board with memory (DDR3-800). It is located on the bottom side of the board. For technical and mechanical reasons it is possible that particular memory modules cannot be employed. Please ask your sales representative for recommended memory modules.

With currently available SO-DIMM modules a memory extension up to 4 GByte is possible. The timing parameters for different memory modules are automatically set by BIOS.

# NOTE

It is not necessary that the memory modules' rated speed and the motherboard's specified memory bus speed match exactly. The system will automatically configure the fastest mutually supported memory bus speed available. For best performance, however, the memory modules' rated speed should be equal to or faster than the motherboard's specified memory bus speed.

| Description              | Name   | Pin |    | Name   | Description     |

|--------------------------|--------|-----|----|--------|-----------------|

| memory reference current | REF-DQ | 1   | 2  | GND    | ground          |

| ground                   | GND    | 3   | 4  | DQ4    | data 4          |

| data 0                   | DQ0    | 5   | 6  | DQ5    | data 5          |

| data 1                   | DQ1    | 7   | 8  | GND    | ground          |

| ground                   | GND    | 9   | 10 | DQS0#  | data strobe 0 - |

| data mask 0              | DM0    | 11  | 12 | DQS0   | data strobe 0 + |

| ground                   | GND    | 13  | 14 | GND    | ground          |

| data 2                   | DQ2    | 15  | 16 | DQ6    | data 6          |

| data 3                   | DQ3    | 17  | 18 | DQ7    | data 7          |

| ground                   | GND    | 19  | 20 | GND    | ground          |

| data 8                   | DQ8    | 21  | 22 | DQ12   | data 12         |

| data 9                   | DQ9    | 23  | 24 | DQ13   | data 13         |

| ground                   | GND    | 25  | 26 | GND    | ground          |

| data strobe 1 -          | DQS1#  | 27  | 28 | DM1    | data mask 1     |

| data strobe 1 +          | DQS1   | 29  | 30 | RESET# | Reset           |

| ground                   | GND    | 31  | 32 | GND    | ground          |

| data 10                  | DQ10   | 33  | 34 | DQ14   | data 14         |

| data 11                  | DQ11   | 35  | 36 | DQ15   | data 15         |

| Description                 | Name    | F   | in  | Name   | Description          |

|-----------------------------|---------|-----|-----|--------|----------------------|

| ground                      | GND     | 37  | 38  | GND    | ground               |

| data 16                     | DQ16    | 39  | 40  | DQ20   | data 20              |

| data 17                     | DQ17    | 41  | 42  | DQ21   | data 21              |

| ground                      | GND     | 43  | 44  | GND    | ground               |

| data strobe 2 -             | DQS2#   | 45  | 46  | DM2    | data mask 2          |

| data strobe 2 +             | DQS2    | 47  | 48  | GND    | ground               |

| ground                      | GND     | 49  | 50  | DQ22   | data 22              |

| data 18                     | DQ18    | 51  | 52  | DQ23   | data 23              |

| data 19                     | DQ19    | 53  | 54  | GND    | ground               |

| ground                      | GND     | 55  | 56  | DQ28   | data 28              |

| data 24                     | DQ24    | 57  | 58  | DQ29   | data 29              |

| data 25                     | DQ25    | 59  | 60  | GND    | ground               |

| ground                      | GND     | 61  | 62  | DQS3#  | data strobe 3 -      |

| data mask 3                 | DQM3    | 63  | 64  | DQS3   | data strobe 3 +      |

| ground                      | GND     | 65  | 66  | GND    | ground               |

| data 26                     | DQ26    | 67  | 68  | DQ30   | data 30              |

| data 27                     | DQ27    | 69  | 70  | DQ31   | data 31              |

| ground                      | GND     | 71  | 72  | GND    | ground               |

| clock enables 0             | CKE0    | 73  | 74  | CKE1   | clock enables 1      |

| 1.5 volt supply             | 1.5V    | 75  | 76  | 1.5V   | 1.5 volt supply      |

| reserved                    | N/C     | 77  | 78  | (A15)  | reserved             |

| SDRAM bank 2                | BA2     | 79  | 80  | A14    | address 14           |

| 1.5 volt supply             | 1.5V    | 81  | 82  | 1.5V   | 1.5 volt supply      |

| address 12 (burst chop)     | A12/BC# | 83  | 84  | A11    | address 11           |

| address 9                   | A9      | 85  | 86  | A7     | address 7            |

| 1.5 volt supply             | 1.5V    | 87  | 88  | 1.5V   | 1.5 volt supply      |

| address 8                   | A8      | 89  | 90  | A6     | address 6            |

| address 5                   | A5      | 91  | 92  | A4     | address 4            |

| 1.5 volt supply             | 1.5V    | 93  | 94  | 1.5V   | 1.5 volt supply      |

| address 3                   | A3      | 95  | 96  | A2     | address 2            |

| address 1                   | A1      | 97  | 98  | A0     | address 0            |

| 1.5 volt supply             | 1.5V    | 99  | 100 | 1.5V   | 1.5 volt supply      |

| Clock 0 +                   | CK0     | 101 | 102 | CK1    | clock 1 +            |

| Clock 0 -                   | CK0#    | 103 | 104 | CK1#   | clock 1 -            |

| 1.5 volt supply             | 1.5V    | 105 | 106 | 1.5V   | 1.5 volt supply      |

| address 10 (auto precharge) | A10/AP  | 107 | 108 | BA1    | SDRAM bank 1         |

| SDRAM Bank 0                | BA0     | 109 | 110 | RAS#   | row address strobe   |

| 1.5 volt supply             | 1.5V    | 111 | 112 | 1.5V   | 1.5 volt supply      |

| write enable                | WE#     | 113 | 114 | S0#    | chip select 0        |

| column address strobe       | CAS#    | 115 | 116 | ODT0   | on die termination 0 |

| 1.5 volt supply             | 1.5V    | 117 | 118 | 1.5V   | 1.5 volt supply      |

| address 13                  | A13     | 119 | 120 | ODT1   | on die termination 1 |

| Chip Select 1               | S1#     | 121 | 122 | N/C    | reserved             |

| 1.5 volt supply             | 1.5V    | 123 | 124 | 1.5V   | 1.5 volt supply      |

| reserved                    | (TEST)  | 125 | 126 | REF-CA | reference current    |

| ground                      | GND     | 127 | 128 | GND    | ground               |

| data 32                     | DQ32    | 129 | 130 | DQ36   | data 36              |

| data 33                     | DQ33    | 131 | 132 | DQ37   | data 37              |

| ground                      | GND     | 133 | 134 | GND    | ground               |

| data strobe 4 -             | DQS4#   | 135 | 136 | DQM4   | data mask 4          |

| data strobe 4 +             | DQS4    | 137 | 138 | GND    | ground               |

| ground                      | GND     | 139 | 140 | DQ38   | data 38              |

| data 34                     | DQ34    | 141 | 142 | DQ39   | data 39              |

| data 35                     | DQ35    | 143 | 144 | GND    | ground               |

| ground                      | GND     | 145 | 146 | DQ44   | data 44              |

| 9.04.14                     | 0.10    | 10  | 1   | J Q    |                      |

Memory Chapter: Connectors

| Description         | Name  | Р   | in  | Name   | Description         |

|---------------------|-------|-----|-----|--------|---------------------|

| data 40             | DQ40  | 147 | 148 | DQ45   | data 45             |

| data 41             | DQ41  | 149 | 150 | GND    | ground              |

| ground              | GND   | 151 | 152 | DQS5#  | data strobe 5 -     |

| data mask 5         | DQM5  | 153 | 154 | DQS5   | data strobe 5 +     |

| ground              | GND   | 155 | 156 |        | ground              |

| data 42             | DQ42  | 157 | 158 | DQ46   | data 46             |

| data 43             | DQ43  | 159 | 160 | DQ47   | data 47             |

| ground              | GND   | 161 | 162 | GND    | ground              |

| data 48             | DQ48  | 163 | 164 | DQ52   | data 52             |

| data 49             | DQ49  | 165 | 166 | DQ53   | data 53             |

| ground              | GND   | 167 | 168 | GND    | ground              |

| data strobe 6 -     | DQS6# | 169 | 170 | DQM6   | data mask 6         |

| data strobe 6       | DQS6  | 171 | 172 | GND    | ground              |

| ground              | GND   | 173 | 174 | DQ54   | data 54             |

| data 50             | DQ50  | 175 | 176 | DQ55   | data 55             |

| data 51             | DQ51  | 177 | 178 | GND    | ground              |

| ground              | GND   | 179 | 180 | DQ60   | data 60             |

| data 56             | DQ56  | 181 | 182 | DQ61   | data 61             |

| data 57             | DQ57  | 183 | 184 | GND    | ground              |

| ground              | GND   | 185 | 186 | DQS7#  | data strobe 7 -     |

| data mask 7         | DQM7  | 187 | 188 | DQS7   | data strobe 7 +     |

| ground              | GND   | 189 | 190 | GND    | ground              |

| data 58             | DQ58  | 191 | 192 | DQ62   | data 62             |

| data 59             | DQ59  | 193 | 194 | DQ63   | data 63             |

| ground              | GND   | 195 | 196 | GND    | ground              |

| SPD address 0       | SA0   | 197 | 198 | EVENT# | Event               |

| 3.3 volt supply     | 3.3V  | 199 | 200 | SDA    | SMBus data          |

| SPD address 1       | SA1   | 201 | 202 | SCL    | SMBus clock         |

| termination current | VTT   | 203 | 204 | VTT    | termination current |

Chapter: Connectors PC/104-Plus Bus

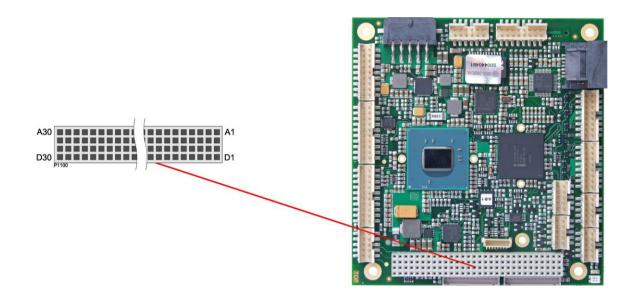

# 3.5 PC/104-Plus Bus

Expansion cards can be connected to the board using the PCI connector first introduced with the PC/104-Plus standard. A maximum of four PC/104-Plus cards are supported.

The interrupt routing and the IDSEL signals for the expansion cards are specified in the PC/104-Plus specification (see "Specifications and Documents", p. 12).

| Description                | Name   | Р   | in  | Name  | Description                |

|----------------------------|--------|-----|-----|-------|----------------------------|

| ground                     | GND    | A1  | B1  | N/C   | reserved                   |

| 3.3 volt - IO buffer power | VIO    | A2  | B2  | AD2   | PCI – address/data 2       |

| PCI – address/data 5       | AD5    | A3  | B3  | GND   | ground                     |

| PCI – com/byte enable 0    | CBE0#  | A4  | B4  | AD7   | PCI – address/data 7       |

| ground                     | GND    | A5  | B5  | AD9   | PCI – address/data 9       |

| PCI – address/data 11      | AD11   | A6  | B6  | VIO   | 3.3 volt - IO buffer power |

| PCI – address/data 14      | AD14   | A7  | B7  | AD13  | PCI – address/data 13      |

| 3.3 volt supply            | 3.3V   | A8  | B8  | CBE1# | PCI – com/byte enable 1    |

| PCI – system error         | SERR#  | A9  | B9  | GND   | ground                     |

| ground                     | GND    | A10 | B10 | PERR# | PCI – parity error         |

| PCI – stop                 | stop#  | A11 | B11 | 3.3V  | 3.3 volt supply            |

| 3.3 volt supply            | 3.3V   | A12 | B12 | TRDY# | PCI – target ready         |

| PCI – frame                | FRAME# | A13 | B13 | GND   | ground                     |

| ground                     | GND    | A14 | B14 | AD16  | PCI – address/data 16      |

| PCI – address/data 18      | AD18   | A15 | B15 | 3.3V  | 3.3 volt supply            |

| PCI – address/data 21      | AD21   | A16 | B16 | AD20  | PCI – address/data 20      |

| 3.3 volt supply            | 3.3V   | A17 | B17 | AD23  | PCI – address/data 23      |

| PCI – ID select slot 1     | IDSEL0 | A18 | B18 | GND   | ground                     |

| PCI – address/data 24      | AD24   | A19 | B19 | CBE3# | PCI – com/byte enable 3    |

| ground                     | GND    | A20 | B20 | AD26  | PCI – address/data 26      |

| PCI – address/data 29      | AD29   | A21 | B21 | VCC   | 5 volt supply              |

| 5 volt supply              | VCC    | A22 | B22 | AD30  | PCI – address/data 30      |

| PCI – bus request slot 1   | REQ0#  | A23 | B23 | GND   | ground                     |

| ground                     | GND    | A24 | B24 | REQ2# | PCI – bus request slot 3   |

| PCI – bus grant slot 4     | GNT1#  | A25 | B25 | VIO   | 5 volt - IO buffer power   |

| 5 volt supply              | VCC    | A26 | B26 | CLK0  | PCI – clock slot 1         |

| PCI – clock slot 3         | CLK2   | A27 | B27 | VCC   | 5 volt supply              |

PC/104-Plus Bus Chapter: Connectors

| Description                | Name   |     | D:  | Nome    | December 1 and 1           |

|----------------------------|--------|-----|-----|---------|----------------------------|

| Description                | Name   |     | Pin | Name    | Description                |

| ground                     | GND    | A28 | B28 | INTD#   | PCI – interrupt D          |

| 12V supply                 | 12V    | A29 | B29 | INTA#   | PCI – interrupt A          |

| -12V supply                | -12V   | A30 | B30 | REQ3#   | PCI – bus request slot 4   |

| 5 volt supply              | VCC    | C1  | D1  | AD0     | PCI – address/data 0       |

| PCI – address/data 1       | AD1    | C2  | D2  | VCC     | 5 volt supply              |

| PCI – address/data 4       | AD4    | C3  | D3  | AD3     | PCI – address/data 3       |

| ground                     | GND    | C4  | D4  | AD6     | PCI – address/data 6       |

| PCI – address/data 8       | AD8    | C5  | D5  | GND     | ground                     |

| PCI – address/data 10      | AD10   | C6  | D6  | M66EN   | PCI – 66MHz enable         |

| ground                     | GND    | C7  | D7  | AD12    | PCI – address/data 12      |

| PCI – address/data 15      | AD15   | C8  | D8  | 3.3V    | 3.3 volt supply            |

| reserved                   | N/C    | C9  | D9  | PAR     | PCI – parity bit           |

| 3.3 volt supply            | 3.3V   | C10 | D10 | N/C     | reserved                   |

| PCI – lock                 | LOCK#  | C11 | D11 | GND     | ground                     |

| ground                     | GND    | C12 | D12 | DEVSEL# | PCI – device select        |

| PCI – initiator ready      | IRDY#  | C13 | D13 | 3.3V    | 3.3 volt supply            |

| 3.3 volt supply            | 3.3V   | C14 | D14 | CBE2#   | PCI – com/byte enable 2    |

| PCI – address/data 17      | AD17   | C15 | D15 | GND     | ground                     |

| ground                     | GND    | C16 | D16 | AD19    | PCI – address/data 19      |

| PCI – address/data 22      | AD22   | C17 | D17 | 3.3V    | 3.3 volt supply            |

| PCI – ID select slot 2     | IDSEL1 | C18 | D18 | IDSEL2  | PCI – ID select slot 3     |

| 3,3 volt - IO buffer power | VIO    | C19 | D19 | IDSEL3  | PCI – ID select slot 4     |

| PCI – address/data 25      | AD25   | C20 | D20 | GND     | ground                     |

| PCI – address/data 28      | AD28   | C21 | D21 | AD27    | PCI – address/data 27      |

| ground                     | GND    | C22 | D22 | AD31    | PCI – address/data 31      |

| PCI – bus request slot 2   | REQ1#  | C23 | D23 | VIO     | 3,3 volt - IO buffer power |

| 5 volt supply              | VCC    | C24 | D24 | GNT0#   | PCI – bus grant slot 1     |

| PCI – bus grant slot 3     | GNT2#  | C25 | D25 | GND     | ground                     |

| ground                     | GND    | C26 | D26 | CLK1    | PCI – clock slot 2         |

| PCI – clock slot 4         | CLK3   | C27 | D27 | GND     | ground                     |

| 5 volt supply              | VCC    | C28 | D28 | RST#    | PCI – reset                |

| PCI – interrupt B          | INTB#  | C29 | D29 | INTC#   | PCI – interrupt C          |

| PCI – bus grant slot 4     | GNT3#  | C30 | D30 | GND     | ground                     |

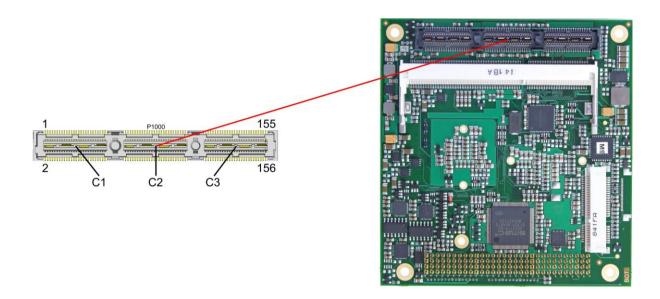

# 3.6 PCI/104-Express Bus

Expansion modules for the PCI-Express bus can be connected to the board using the PCI/104-Express™ connector. This is a "type 2" connector with only those signals connected that are supported by the chipset. "Stacking Error" functionality is available. For specifics, please refer to the PCI/104-Express™ documentation (rev. 2.0).

Pinout PCI104-Express connector (type 2):

| Description           | Name     | Pin |    | Name     | Description           |

|-----------------------|----------|-----|----|----------|-----------------------|

| USB overcurrent       | USBOC#   | 1   | 2  | PERST#   | PCIe reset            |

| 3.3 volt supply       | 3.3V     | 3   | 4  | 3.3V     | 3.3 volt supply       |

| USB11 +               | USB11    | 5   | 6  | USB10    | USB10 +               |

| USB11 -               | USB11#   | 7   | 8  | USB10#   | USB10 -               |

| ground                | GND      | 9   | 10 | GND      | ground                |

| transmit lane 2 +     | PET2     | 11  | 12 | PET1     | transmit Lane 1 +     |

| transmit lane 2 -     | PET2#    | 13  | 14 | PET1#    | transmit lane 1 -     |

| ground                | GND      | 15  | 16 | GND      | ground                |

| transmit lane 3 +     | PET3     | 17  | 18 | PET4     | transmit lane 4 +     |

| transmit lane 3 -     | PET3#    | 19  | 20 | PET4#    | transmit lane 4 -     |

| ground                | GND      | 21  | 22 | GND      | ground                |

| receive lane 2 +      | PER2     | 23  | 24 | PER1     | receive lane 1 +      |

| receive lane 2 -      | PER2#    | 25  | 26 | PER1#    | receive lane 1 -      |

| ground                | GND      | 27  | 28 | GND      | ground                |

| receive lane 3 +      | PER3     | 29  | 30 | PER4     | receive lane 4 +      |

| receive lane 3 -      | PER3#    | 31  | 32 | PER4#    | receive lane 4 -      |

| ground                | GND      | 33  | 34 | GND      | ground                |

| clock slot 1 +        | PECLK1   | 35  | 36 | PECLK0   | clock slot 0 +        |

| clock slot 1 -        | PECLK1#  | 37  | 38 | PECLK0#  | clock slot 0 -        |

| 5 volt standby supply | SVCC     | 39  | 40 | SVCC     | 5 volt standby supply |

| clock slot 2 +        | PECLK2   | 41  | 42 | PECLK3   | clock slot 3 +        |

| clock slot 2 -        | PECLK2#  | 43  | 44 | PECLK3#  | clock slot 3 -        |

| CPU direction         | CPU_DIR  | 45  | 46 | PWRGOOD  | powergood             |

| SMBus data            | SMBDAT   | 47  | 48 | N/C      | reserved              |

| SMBus clock           | SMBCLK   | 49  | 50 | N/C      | reserved              |

| SMBus alert           | SMBALERT | 51  | 52 | PSON#    | power supply on       |

| link reactivation     | PEWAKE#  | 53  | 54 | ST1-ERR# | stacking error 1      |

**Chapter:** Connectors

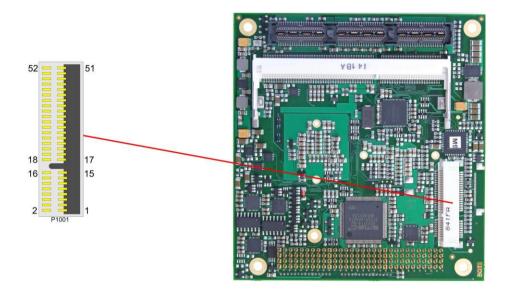

# 3.7 PCI-Express Mini Card

As a soldering option, the CB4057 can be equipped with PCI-Express Mini Card connector to interface with approved peripherals, such as Wi-FI and storage cards.

| Description             | Name      | Pin |    | Name      | Description             |

|-------------------------|-----------|-----|----|-----------|-------------------------|

| PCIe ake                | PEWAKE#   | 1   | 2  | S3.3V     | 3.3 volt standby supply |

| reserved                | N/C       | 3   | 4  | GND       | ground                  |

| reserved                | N/C       | 5   | 6  | 1.5V      | 1.5 volt supply         |

| clock enable            | PEMCLKen# | 7   | 8  | N/C       | reserved                |

| ground                  | GND       | 9   | 10 | N/C       | reserved                |

| clock -                 | PECLKMC#  | 11  | 12 | N/C       | reserved                |

| clock +                 | PECLKMC   | 13  | 14 | N/C       | reserved                |

| ground                  | GND       | 15  | 16 | N/C       | reserved                |

| reserved                | N/C       | 17  | 18 | GND       | ground                  |

| reserved                | N/C       | 19  | 20 | WDISABLE# | wireless disable        |

| ground                  | GND       | 21  | 22 | PERST#    | PCIe reset              |

| PCIe receive -          | PERMC#    | 23  | 24 | S3.3V     | 3.3 volt standby supply |

| PCIe receive +          | PERMC     | 25  | 26 | GND       | ground                  |

| ground                  | GND       | 27  | 28 | 1.5V      | 1.5 volt supply         |

| ground                  | GND       | 29  | 30 | SMB-CLK   | SM-bus clock            |

| PCIe transmit -         | PETMC#    | 31  | 32 | SMB-DAT   | SM-bus data             |

| PCIe transmit +         | PETMC     | 33  | 34 | GND       | ground                  |

| ground                  | GND       | 35  | 36 | USBMC#    | USB -                   |

| ground                  | GND       | 37  | 38 | USBMC     | USB +                   |

| 3.3 volt standby supply | S3.3V     | 39  | 40 | GND       | ground                  |

| 3.3 volt standby supply | S3.3V     | 41  | 42 | N/C       | reserved                |

| ground                  | GND       | 43  | 44 | N/C       | reserved                |

| reserved                | N/C       | 45  | 46 | N/C       | reserved                |

| reserved                | N/C       | 47  | 48 | 1.5V      | 1.5 volt supply         |

| reserved                | N/C       | 49  | 50 | GND       | ground                  |

| reserved                | N/C       | 51  | 52 | S3.3V     | 3.3 volt standby supply |

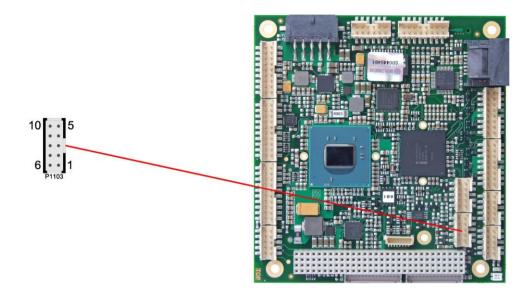

VGA Chapter: Connectors

# 3.8 VGA

The CRT-VGA signals are provided by a 2x5pin connector (FCI 98424-G52-10LF, mating connector e.g. FCI 90311-010LF).

This interface allows the connection of a standard VGA-monitor. I2C communication is supported.

| Description     | Name  | Pin |    | Name | Description |

|-----------------|-------|-----|----|------|-------------|

| analog red      | RED   | 1   | 6  | GND  | ground      |

| analog green    | GREEN | 2   | 7  | DDDA | DD data     |

| analog blue     | BLUE  | 3   | 8  | DDCK | DD clock    |

| vertikal sync   | VSYNC | 4   | 9  | GND  | ground      |

| horizontal sync | HSYNC | 5   | 10 | GND  | ground      |

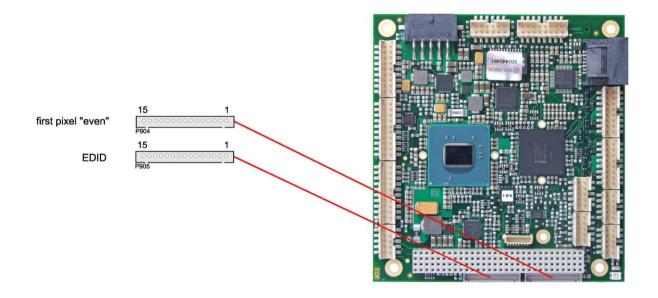

Chapter: Connectors LCD

#### 3.9 LCD

The LCD is connected via two 15 pin connectors (Hirose DF13-15P-1.25DSA, mating connector: DF13-15S-xxx). The power supply for the display is also provided through these connectors. The CB4057 board only supports displays with LVDS interface. For displays with digital interface an extra receiver board is available. There is no support for DSTN displays.

With the LVDS interface it is possible to trigger LVDS displays with a maximum of 18 Bit colour depth and one or two pixels per clock. For single pixel displays only one connector is necessary. However, if you want to read the display's EDID data the second connector must be connected.

The display type can be chosen over the BIOS setup. Please contact your sales representative regarding an appropriate cable to connect your display.

The following table shows the pin description for the first bit ("even" pixel).

| Pin | Name    | Description                   |

|-----|---------|-------------------------------|

| 1   | GND     | ground                        |

| 2   | GND     | ground                        |

| 3   | TXO00#  | LVDS even data 0 -            |

| 4   | TXO00   | LVDS even data 0 +            |

| 5   | TXO01#  | LVDS even data 1 -            |

| 6   | TXO01   | LVDS even data 1 +            |

| 7   | TXO02#  | LVDS even data 2 -            |

| 8   | TXO02   | LVDS even data 2 +            |

| 9   | TXO0C#  | LVDS even clock -             |

| 10  | TXO0C   | LVDS even clock +             |

| 11  | N/C     | reserved                      |

| 12  | N/C     | reserved                      |

| 13  | BL_VCC  | switched 5 volt for backlight |

| 14  | FP_3.3V | switched 3.3 volt for display |

| 15  | FP_3.3V | switched 3.3 volt for display |

LCD Chapter: Connectors

The following table shows the pin description for the second connector used for evaluating the display's EDID data.

| Pin | Name    | Description        |

|-----|---------|--------------------|

| 1   | GND     | ground             |

| 2   | GND     | ground             |

| 3   | N/C     | reserved           |

| 4   | N/C     | reserved           |

| 5   | N/C     | reserved           |

| 6   | N/C     | reserved           |

| 7   | N/C     | reserved           |

| 8   | N/C     | reserved           |

| 9   | N/C     | reserved           |

| 10  | N/C     | reserved           |

| 11  | N/C     | reserved           |

| 12  | N/C     | reserved           |

| 13  | DDC_CLK | EDID clock for LCD |

| 14  | DDC_DAT | EDID data for LCD  |

| 15  | VCC     | 5 volt supply      |

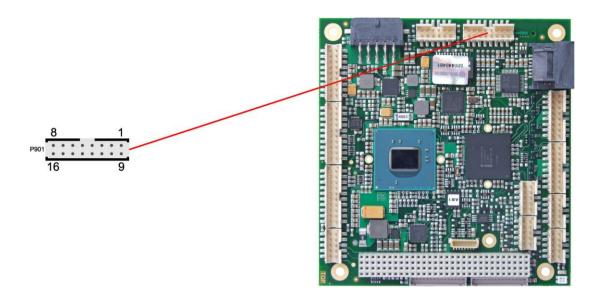

Chapter: Connectors Audio

# 3.10 Audio

The CB4057's audio functions are provided via a 2x8pin connector (FCI 98424-G52-16LF, mating connector e.g. FCI 90311-016LF). This interface provides eight output channels for full 7.1 sound output. Two microphone inputs and two AUX inputs are also available.

The signals "SPDIFI" and "SPDIFO" provide digital input and output. If a transformation to a coaxial or optical connector is necessary this must be performed externally.

| Description             | Name    | Pin |    | Name    | Description            |

|-------------------------|---------|-----|----|---------|------------------------|

| digital output SPDIF    | SPDIFO  | 1   | 9  | 3.3V    | 3.3 volt supply        |

| digital input SPDIF     | SPDIFI  | 2   | 10 | S_AGND  | analog ground sound    |

| sound output right      | LOUT_R  | 3   | 11 | LOUT_L  | sound output left      |

| AUX input right         | AUXA_R  | 4   | 12 | AUXA_L  | AUX input left         |

| microphone input 1      | MIC1    | 5   | 13 | MIC2    | microphone input 2     |

| surround out right      | SOUT_R  | 6   | 14 | SOUT_L  | surround out left      |

| center output           | CENOUT  | 7   | 15 | LFEOUT  | LFE output             |

| side surround out right | SSOUT_R | 8   | 16 | SSOUT_L | side surround out left |

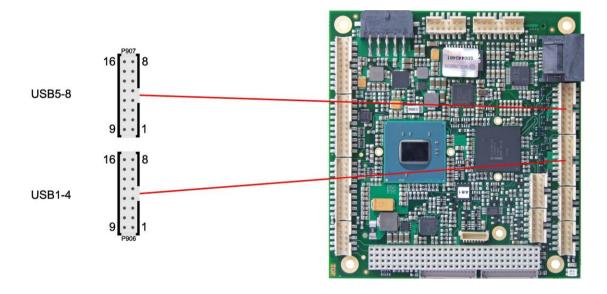

USB Chapter: Connectors

# 3.11 USB

USB channels 1 to 8 are provided via two 2x8pin connectors (FCI 98424-G52-16LF, mating connector e.g. FCI 90311-016LF).

All USB-channels support USB 2.0. You may note that the setting of USB keyboard or USB mouse support in the BIOS-setup is only necessary and advisable, if the OS offers no USB-support. BIOS-setup can be changed with a USB keyboard without enabling USB keyboard support. Running a USB supporting OS (such as Microsoft® Windows®) with these features enabled may lead to significant performance or functionality limitations.

Every USB interface provides up to 500 mA current and is protected by an electronically resettable fuse.

### NOTE

There are two more USB channels available on the PCI104-Express connector (p. 22) and another one on the Mini Card connector (if populated, p. 24).

Pinout USB 1-4:

| Description        | Name     | Pin |    | Name    | Description        |

|--------------------|----------|-----|----|---------|--------------------|

| 5 volt for USB1    | USB1 VCC | 1   | 9  | USB2VCC | 5 volt for USB2    |

| minus channel USB1 | USB1#    | 2   | 10 | USB2#   | minus channel USB2 |

| plus channel USB1  | USB1     | 3   | 11 | USB2    | plus channel USB2  |

| ground             | GND      | 4   | 12 | GND     | ground             |

| ground             | GND      | 5   | 13 | GND     | ground             |

| plus channel USB3  | USB3     | 6   | 14 | USB4    | plus channel USB4  |

| minus channel USB3 | USB3#    | 7   | 15 | USB4#   | minus channel USB4 |

| 5 volt for USB3    | USB3VCC  | 8   | 16 | USB4VCC | 5 volt for USB4    |

Chapter: Connectors USB

#### Pinout USB 5-8:

| Description        | Name     |   | Pin | Name    | Description        |

|--------------------|----------|---|-----|---------|--------------------|

| 5 volt for USB5    | USB5 VCC | 1 | 9   | USB6VCC | 5 volt for USB6    |

| minus channel USB5 | USB5#    | 2 | 10  | USB6#   | minus channel USB6 |

| plus channel USB5  | USB5     | 3 | 11  | USB6    | plus channel USB6  |

| ground             | GND      | 4 | 12  | GND     | ground             |

| ground             | GND      | 5 | 13  | GND     | ground             |

| plus channel USB7  | USB7     | 6 | 14  | USB8    | plus channel USB8  |

| minus channel USB7 | USB7#    | 7 | 15  | USB8#   | minus channel USB8 |

| 5 volt for USB7    | USB7VCC  | 8 | 16  | USB8VCC | 5 volt for USB8    |

LAN Chapter: Connectors

# 3.12 LAN

The LAN interface is provided via a 2x6pin connector (FCI 98424-G52-12LF, mating connector e.g. FCI 90311-012LF). The interface supports 10BaseT, 100BaseT, and 1000BaseT compatible network components with automatic bandwidth selection. Additional outputs are provided for status LEDs. Auto-negotiate and auto-cross functionality is available, PXE and RPL are available on request.

#### Pinout LAN interface:

| Description         | Name     | Pin |    | Name      | Description         |

|---------------------|----------|-----|----|-----------|---------------------|

| LAN activity        | LINKACT  | 1   | 7  | SPEED1000 | LAN speed 1000Mbit  |

| LAN channel 1 plus  | LAN1     | 2   | 8  | LAN0      | LAN channel 0 plus  |

| LAN channel 1 minus | LAN1#    | 3   | 9  | LAN0#     | LAN channel 0 minus |

| LAN channel 3 plus  | LAN3     | 4   | 10 | LAN2      | LAN channel 2 plus  |

| LAN channel 3 minus | LAN3#    | 5   | 11 | LAN2#     | LAN channel 2 minus |

| LAN speed 100Mbit   | SPEED100 | 6   | 12 | 3.3V      | 3.3 volt supply     |

Chapter: Connectors SATA Interfaces

# 3.13 SATA Interfaces

The CB4057 provides two SATA interfaces allowing transfer rates of up to 3 Gbit per second. These interfaces are made available via two 7 pin connectors.

The required settings are made in the BIOS setup.

# NOTE

There are two more SATA channels available on the PCI104-Express connector (p. 22), extending the available RAID options to 0/1/5/10.

#### Pinout SATA:

| Pin | Name    | Description     |

|-----|---------|-----------------|

| 1   | GND     | ground          |

| 2   | SATATX  | SATA transmit + |

| 3   | SATATX# | SATA transmit - |

| 4   | GND     | ground          |

| 5   | SATARX  | SATA receive +  |

| 6   | SATARX# | SATA receive -  |

| 7   | GND     | ground          |

COM1 and COM2 Chapter: Connectors

# **3.14 COM1 and COM2**

The serial interfaces COM1 and COM2 are provided via a 2x5pin connector (FCI 98424-G52-10LF, mating connector e.g. FCI 90311-010LF).

| Description         | Name | Pin |    | Name | Description     |

|---------------------|------|-----|----|------|-----------------|

| data carrier detect | DCD  | 1   | 6  | DSR  | data set ready  |

| receive data        | RXD  | 2   | 7  | RTS  | request to send |

| transmit data       | TXD  | 3   | 8  | CTS  | clear to send   |

| data terminal ready | DTR  | 4   | 9  | RI   | ring indicator  |

| ground              | GND  | 5   | 10 | VCC  | 5 volt supply   |

Chapter: Connectors COM3 and COM4

# 3.15 COM3 and COM4

The serial interfaces COM3 and COM4 are provided via a 2x5pin connector (FCI 98424-G52-10LF, mating connector e.g. FCI 90311-010LF). For these two interfaces, both RS232 and RS485 protocols are available. This can be configured in BIOS setup.

| Description         | Name |   | Pin | Name | Description     |

|---------------------|------|---|-----|------|-----------------|

| data carrier detect | DCD  | 1 | 6   | DSR  | data set ready  |

| receive data        | RXD  | 2 | 7   | RTS  | request to send |

| transmit data       | TXD  | 3 | 8   | CTS  | clear to send   |

| data terminal ready | DTR  | 4 | 9   | RI   | ring indicator  |

| ground              | GND  | 5 | 10  | VCC  | 5 volt supply   |

#### Pinout in RS422/485 mode:

| Description     | Name |   | Pin | Name | Description     |

|-----------------|------|---|-----|------|-----------------|

| transmit data + | TX   | 1 | 6   | TX#  | transmit data - |

| receive data +  | RX   | 2 | 7   | RX#  | receive data -  |

| reserved        | N/C  | 3 | 8   | N/C  | reserved        |

| reserved        | N/C  | 4 | 9   | N/C  | reserved        |

| ground          | GND  | 5 | 10  | VCC  | 5 volt supply   |

# NOTE

Proper use of RS485 requires that the signal RTS (Request To Send) be toggled on an off in order to turn on and off the transmit function. It is the responsibility of the software application to assert control over the RTS line.

Parallel Interface LPT Chapter: Connectors

# 3.16 Parallel Interface LPT

The parallel interface is a 2x10pin connector (FCI 98424-G52-20LF, mating connector e.g. FCI 90311-020LF). The port address and the interrupt are set via the BIOS setup.

Pinout LPT:

| Description   | Name | Pin |    | Name  | Description         |

|---------------|------|-----|----|-------|---------------------|

| strobe        | STB# | 1   | 11 | AFD#  | automatic line feed |

| LPT data 0    | PD0  | 2   | 12 | ERR#  | error               |

| LPT data 1    | PD1  | 3   | 13 | INIT# | init                |

| LPT data 2    | PD2  | 4   | 14 | SLIN# | select input        |

| LPT data 3    | PD3  | 5   | 15 | SLCT  | select printer      |

| LPT data 4    | PD4  | 6   | 16 | PE    | paper end           |

| LPT data 5    | PD5  | 7   | 17 | BUSY  | busy                |

| LPT data 6    | PD6  | 8   | 18 | ACK#  | acknowledge         |

| LPT data 7    | PD7  | 9   | 19 | GND   | ground              |

| 5 volt supply | VCC  | 10  | 20 | GND   | ground              |

Chapter: Connectors GPIO

# 3.17 **GPIO**

The General Purpose Input/Output interface is made available through a 2x10 pin connector (FCI 98424-G52-20LF, mating connector e.g. FCI 90311-020LF). To make use of this interface the SIO unit must be programmed accordingly. Please refer to your sales representative for information on available software support.

| Description        | Name   |    | Pin | Name   | Description        |

|--------------------|--------|----|-----|--------|--------------------|

| ground             | GND    | 1  | 11  | 3.3V   | 3.3 volt supply    |

| GP input/output 00 | GPIO00 | 2  | 12  | GPIO10 | GP input/output 10 |

| GP input/output 01 | GPIO01 | 3  | 13  | GPIO11 | GP input/output 11 |

| GP input/output 02 | GPIO02 | 4  | 14  | GPIO12 | GP input/output 12 |

| GP input/output 03 | GPIO03 | 5  | 15  | GPIO13 | GP input/output 13 |

| GP input/output 04 | GPIO04 | 6  | 16  | GPIO14 | GP input/output 14 |

| GP input/output 05 | GPIO05 | 7  | 17  | GPIO15 | GP input/output 15 |

| GP input/output 06 | GPIO06 | 8  | 18  | GPIO16 | GP input/output 16 |

| GP input/output 07 | GPIO07 | 9  | 19  | GPIO17 | GP input/output 17 |

| 3.3 volt supply    | 3.3V   | 10 | 20  | GND    | ground             |

Monitoring Functions Chapter: Connectors

### 3.18 Monitoring Functions

Additional monitoring functions, such as the status of the fan or of other devices connected over SM-Bus (e. g. temperature sensor), are accessible via an 8 pin connector (JST BM08B-SRSS-TB, mating connector: SHR-08V-S(-B)).

| Pin | Name       | Description              |

|-----|------------|--------------------------|

| 1   | 3.3V       | 3.3 volt supply          |

| 2   | CS-SMB-CLK | SMBus clock              |

| 3   | CS-SMB-DAT | SMBus data               |

| 4   | GND        | ground                   |

| 5   | FANON1     | 5 volt supply (switched) |

| 6   | FANCTRL1   | fan 1 monitoring signal  |

| 7   | VCC        | 5 volt supply            |

| 8   | FANCTRL3   | fan 3 monitoring signal  |

Chapter: Status LEDs HD LED

# 4 Status LEDs

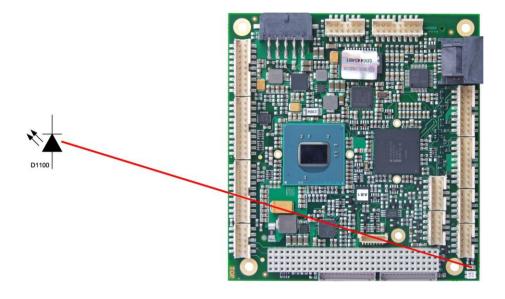

### **4.1 HD LED**

Harddisk activity is signalled by a dedicated LED.

RGB LED Chapter: Status LEDs

### 4.2 RGB LED

The CB4057 has an RGB LED, which can signal status messages by using different colors and flash intervals.

#### Status Codes RGB LED:

| Color        | Interval        | Meaning                                                                                           |

|--------------|-----------------|---------------------------------------------------------------------------------------------------|

| none         | solid           | Invalid system state                                                                              |

| White        | solid           | The microcontroller has just been flashed and is being prepared for normal operation after reboot |

| Cyan         | solid           | Reserved                                                                                          |

| Magenta      | solid           | Reserved                                                                                          |

| Blue         | solid           | Reserved                                                                                          |

| Yellow       | solid           | Reserved                                                                                          |

| Green        | solid           | Board operates normal                                                                             |

| Red          | solid           | Board is in Reset                                                                                 |

| Green/Yellow | flashing        | Bootloader operates normal                                                                        |

| Red          | flashing        | Firmware is being started (start sequence still running)                                          |

| Red/Yellow   | flashing        | Bootloader is being started (start sequence still running)                                        |

| Red/Magenta  | flashing        | Checksum error during I2C transmission in bootloader                                              |

| Red/Blue     | flashing        | Update completed, waiting for manual Reset                                                        |

| Yellow       | flashing (10s)  | S5 state                                                                                          |

| Yellow       | flashing (6s)   | S4 state                                                                                          |

| Yellow       | flashing (3s)   | Reserved                                                                                          |

| Yellow       | flashing (0.5s) | Reserved                                                                                          |

# Note

If the board appears to be in Reset (Red LED lit) then this could also indicate a PCI104-Express "stacking error". Such an error could occur when the stack contains a peripheral card which has the wrong type of connector (PCI104-Express Type 1 instead of Type 2 or vice versa).

### 5 BIOS Settings

**Chapter:** BIOS Settings

### 5.1 Remarks for Setup Use

In a setup page, standard values for its setup entries can be loaded. Fail-safe defaults are loaded with F6 and optimized defaults are loaded with F7. These standard values are independent of the fact that a board has successfully booted with a setup setting before.

This is different if these defaults are called from the Top Menu. Once a setup setting was saved, which subsequently leads to a successful boot process, those values are loaded as default for all setup items afterwards.

See also the chapters "Load Fail-Safe Defaults" (5.10) and "Load Optimized Defaults" (5.11).

#### NOTE

BIOS features and setup options are subject to change without notice. The settings displayed in the screenshots on the following pages are meant to be examples only. They do not represent the recommended settings or the default settings. Determination of the appropriate settings is dependent upon the particular application scenario in which the board is used.

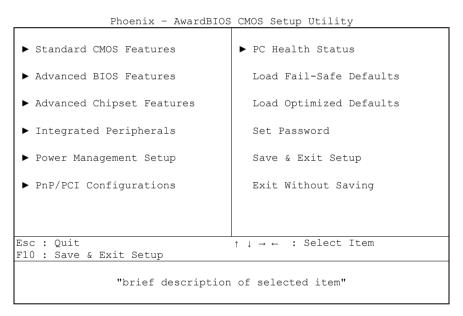

### 5.2 Top Level Menu

The sign "▶" in front of an item means that there is a sub menu.

The "x" sign in front of an item means, that the item is disabled but can be enabled by changing or selecting some other item (usually somewhere above the disabled item on the same screen).

Use the arrow buttons to navigate from one item to another. For selecting an item press Enter which will open either a sub menu or a dialog screen.

### 5.3 Standard CMOS Features

Phoenix - AwardBIOS CMOS Setup Utility Standard CMOS Features

| Date (mm:dd:yy) | Sat, Jan 15 2011          | Item Help |

|-----------------|---------------------------|-----------|

| Time (hh:mm:ss) | 11 : 13 : 35              | icem neib |

|                 |                           |           |

| ► CAMA 1        | [ Name ]                  |           |

| ► SATA 1        | [ None]                   |           |

| ► SATA 2        | [ None]                   |           |

| Halt On         | [No Errors]               |           |

|                 |                           |           |

| Base Memory     | 639K                      |           |

| Extended Memory | 513024K                   |           |

| Total Memory    | 514048K                   |           |

| TOTAL MEMOLY    | 31404010                  |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 |                           |           |

|                 | . / /27/22 77 1 210 0 200 |           |

11--:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:Help F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

### ✓ Date (mm:dd:yy)

Options: mm: month

dd: day yy: year

#### √ Time (hh:mm:ss)

Options: hh: hours

mm: minutes ss: seconds

#### ✓ SATA 1

Sub menu: see "SATA channels" (p. 42)

#### ✓ SATA 2

Sub menu: see "SATA channels" (p. 42)

#### ✓ Halt On

Options: All Errors / No Errors / All, But Keyboard

### √ Base Memory

Options: none

#### ✓ Extended Memory

Options: none

#### √ Total Memory

Options: none

Chapter: BIOS Settings Standard CMOS Features

#### 5.3.1 SATA channels

Phoenix - AwardBIOS CMOS Setup Utility SATA 1/2

|                        | SAIA I/Z |        |           |

|------------------------|----------|--------|-----------|

| IDE HDD Auto-Detection | [Press   | Enter] | Item Help |

| SATA 1/2               | [Auto]   |        |           |

| Access Mode            | [Auto]   |        |           |

| Capacity               | 0        | MB     |           |

| Cylinder               | 0        |        |           |

| Head                   | 0        |        |           |

| Precomp                | 0        |        |           |

| Landing Zone           | 0        |        |           |

| Sector                 | 0        |        |           |

|                        |          |        |           |

|                        |          |        |           |

|                        |          |        |           |

|                        |          |        |           |

|                        |          |        |           |

† :- : Move Enter: Select +/-/PU/PD: Value F10: Save ESC: Exit F1: Help F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

#### ✓ IDE HDD Auto-Detection

Options: none

#### ✓ SATA 1/2

Options: None / Auto / Manual

#### ✓ Access Mode

Options: CHS / LBA / Large / Auto

Advanced BIOS Features Chapter: BIOS Settings

#### 5.4 Advanced BIOS Features

Phoenix - AwardBIOS CMOS Setup Utility

Advanced BIOS Features

| Hard CPU Hype Quic Firs Seco Thir Boot Gate Type x Type x Type Secu x APIC MPS | nd Boot Device d Boot Device Other Device Up NumLock Status A20 Option matic Rate Setting matic Rate (Chars/Sec) matic Delay (Msec) rity Option Mode Version Control For OS | [Enabled] [Enabled] [Enabled] [USB-FDD] [USB-CDROM] [Hard Disk] [Enabled] [On] [Fast] [Disabled] 6 250 [Setup] Enabled [1.4] | Item Help |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------|

| MPS<br>OS S                                                                    |                                                                                                                                                                             | [1.4]<br>[Non-OS2]                                                                                                           |           |

| _                                                                              | Screen LOGO Show                                                                                                                                                            | [Disabled]                                                                                                                   |           |

11--:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:Help F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

#### ✓ CPU Feature

Sub menu: see "CPU Feature" (p. 45)

#### √ Hard Disk Boot Priority

Sub menu: see "Hard Disk Boot Priority" (p. 46)

### ✓ CPU L3 Cache

Options: Enabled / Disabled

### ✓ Hyper-Threading Technology

Options: Enabled / Disabled

### ✓ Quick Power On Self Test

Options: Enabled / Disabled

#### ✓ First Boot Device

Options: LS120 / Hard Disk / CDROM / ZIP100 / USB-FDD / USB-ZIP / Legacy LAN / Onboard

LAN 00C8 / Disabled

#### ✓ Second Boot Device

Options: LS120 / Hard Disk / CDROM / ZIP100 / USB-FDD / USB-ZIP / Legacy LAN / Onboard

LAN 00C8 / Disabled

#### ✓ Third Boot Device

Options: LS120 / Hard Disk / CDROM / ZIP100 / USB-FDD / USB-ZIP / Legacy LAN / Onboard

LAN 00C8 / Disabled

#### ✓ Boot Other Device

Options: Enabled / Disabled

#### ✓ Boot Up NumLock Status

Options: Off / On

#### ✓ Gate A20 Option

Options: Normal / Fast

#### Chapter: BIOS Settings

Options: Enabled / Disabled

#### ✓ Typematic Rate (Chars/Sec)

**Typematic Rate Setting**

Options: 6/8/10/12/15/20/24/30

### √ Typematic Delay (Msec)

Options: 250 / 500 / 750 / 1000

#### ✓ Security Option

Options: Setup / System

#### ✓ APIC Mode

Options: none

#### ✓ MPS Version Control For OS

Options: 1.1 / 1.4

#### √ OS Select For DRAM > 64MB

Options: Non-OS2 / OS2

#### ✓ Report No FDD For WIN 95

Options: No / Yes

#### ✓ Full Screen LOGO Show

Options: Enabled / Disabled

Advanced BIOS Features Chapter: BIOS Settings

#### 5.4.1 CPU Feature

Phoenix - AwardBIOS CMOS Setup Utility CPU Feature

| Thermal Management                                  | [Thermal Monitor 2]   | Item Help |

|-----------------------------------------------------|-----------------------|-----------|

| Limit CPUID MaxVal C1E Function Execute Disable Bit | [Disabled] [Disabled] |           |

| Execute Disable Bit                                 | [Enabled]             |           |

|                                                     |                       |           |

|                                                     |                       |           |

|                                                     |                       |           |

|                                                     |                       |           |

|                                                     |                       |           |

|                                                     |                       |           |

†|---:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:Help F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

#### √ Thermal Management

Options: Thermal Monitor 1 / Thermal Monitor 2 / Disabled / TM1 + TM2 enabled

#### ✓ Limit CPUID MaxVal

Options: Enabled / Disabled

#### ✓ C1E Function

Options: Auto / Disabled

#### √ Execute Disable Bit

Options: Enabled / Disabled

Chapter: BIOS Settings Advanced BIOS Features

### 5.4.2 Hard Disk Boot Priority

Phoenix - AwardBIOS CMOS Setup Utility Hard Disk Boot Priority

|                  | nara bibk book firefrey |           |

|------------------|-------------------------|-----------|

| 1. Bootable Add- | in Cards                | Item Help |

|                  |                         |           |

|                  |                         |           |

|                  |                         |           |

|                  |                         |           |

|                  |                         |           |

|                  |                         |           |

|                  |                         |           |

|                  |                         |           |

↑↓→-:Move PU/PD/+/-:Change Priority F10:Save ESC:Exit F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

#### √ [list of available devices]

Options: this dialog allows you to set the order in which the available bootable devices shall be accessed for an attempt to boot.

### ✓ Attention!

in this sub menu the buttons <Page Up>, <Page Down>, <+> and <-> have a different function than in the rest of the setup: They serve to move the items of the list up or down.

### 5.5 Advanced Chipset Features

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

| Advanced                     | inipset reatures |           |

|------------------------------|------------------|-----------|

| System BIOS Cacheable        | [Enabled]        | Item Help |

| Memory Hole At 15M-16M       | [Disabled]       | reem nerp |

| ▶ PCI Express Root Port Func | [Press Enter]    |           |

| Disable MCHBAR MMIO          | [Enabled]        |           |

|                              |                  |           |

| ** VGA Setting **            |                  |           |

| On-Chip Frame Buffer Size    | [ 64MB]          |           |

| DVMT Mode                    | [Enable]         |           |

| Total GFX Memory             | [128MB]          |           |

| Boot Display                 | [VBIOS Default]  |           |

| Panel Scaling                | [AUTO]           |           |

| Panel Number                 | [ 800x600]       |           |

|                              |                  |           |

|                              |                  |           |

|                              |                  |           |

|                              |                  |           |

|                              |                  |           |

|                              |                  |           |

|                              |                  |           |

11--:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:Help F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

#### √ System BIOS Cacheable

Options: Enabled / Disabled

#### ✓ Memory Hole At 15M-16M

Options: Enabled / Disabled

#### √ PCI Express Root Port Func

Sub menu: see "PCI Express Root Port Function" (p. 48)

#### ✓ Disable MCHBAR MMIO

Options: Enabled / Disabled

#### ✓ On-Chip Frame Buffer Size

Options: 1MB / 8MB

#### ✓ DVMT Mode

Options: Disable / Enable

#### √ Total GFX Memory

Options: 128MB / 256MB / MAX.

#### ✓ Boot Display

Options: Auto / CRT / LFP

#### ✓ Panel Scaling

Options: Auto / On / Off

#### ✓ Panel Number

Options: 640x480 / 800x600 / 1024x768 / 1280x768 / 1024x768 / 1280x800 / 1280x600

### NOTE

For "Panel Number", some values might occur multiple times in the list. This means that the video signal is available in slightly different configurations, offering the possibility to choose the one which works best with the target display.

Chapter: BIOS Settings

# 5.5.1 PCI Express Root Port Function

Chapter: BIOS Settings

Phoenix - AwardBIOS CMOS Setup Utility PCI Express Root Port Func

|                  | LCI EXPIESS | ROOL POIL FUILC |           |

|------------------|-------------|-----------------|-----------|

| PCI Express Port | 1           | [Auto]          | Item Help |

| PCI Express Port | 2           | [Auto]          | rcem neip |

| PCI Express Port | 3           | [Auto]          |           |

| PCI Express Port | 4           | [Auto]          |           |

| PCI Express Port | 5           | [Auto]          |           |

| PCI-E Compliancy | Mode        | [v1.0a]         |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

|                  |             |                 |           |

↑↓→:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:Help F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

#### ✓ PCI Express Port 1

Options: Auto / Enabled / Disabled

#### ✓ PCI Express Port 2

Options: Auto / Enabled / Disabled